Combinational Logic & Computer Arithmetic Review

COMP 303 PS1

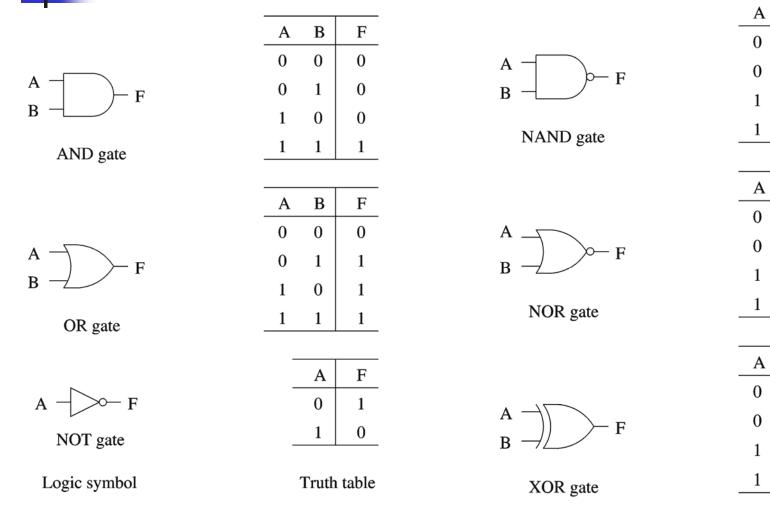

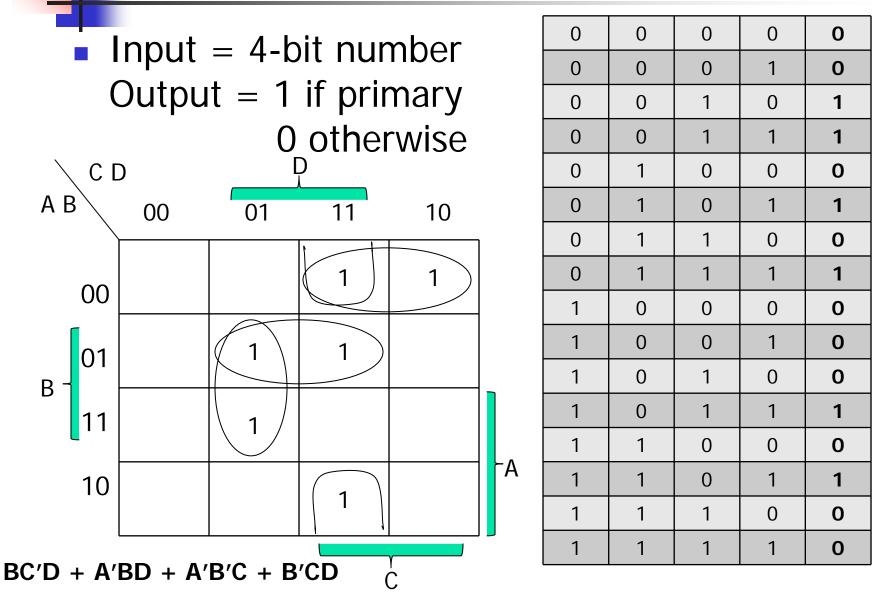

### **Combinational Logic Review**

Truth table

Logic symbol

F

F

F

В

В

В

#### **Combinational Logic Review**

# Shift Operations

The MIPS architecture defines various shift operations:

(a) sll r1, r2, 3 r2 = 10101100 (shift left logical) r1 = 01100000

- shift in zeros to the least significant bits

(b) srl r1, r2, 3 r2 = 10101100 (shift right logical) r1 = 00010101

- shift in zeros to the most significant bits

(c) sra r1, r2, 3 r2 = 10101100 (shift right arithmetic) r1 = 11110101

- copy the sign bit to the most significant bits

There are also versions of these instructions that take three register operands.

# Logical Operations

In the MIPS architecture logical operations (and, or, xor) correspond to bit-wise operations.

(a) and r1, r2, r3 r3 = 1010 (r1 is 1 if r2 and r3 are both one) r2 = 0110 r1 = 0010(b) or r1, r2, r3 r3 = 1010 (r1 is 1 if r2 or r3 is one) r2 = 0110 r1 = 1110(c) xor r1, r2, r3 r3 = 1010 (r1 is 1 if r2 and r3 are different) r2 = 0110r1 = 1100

Immediate versions of these instructions are also supported.

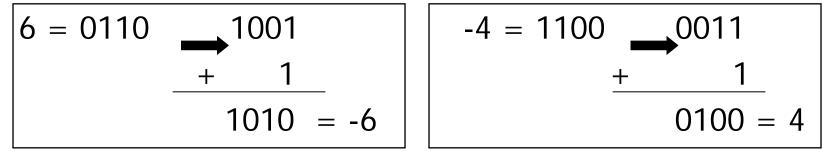

## **Two's Complement Negation**

To negate a two's complement integer, invert all the bits and add a one to the least significant bit.

What are the two's complements of

#### **Two's Complement Subtraction**

To subtract two's complement numbers we first negate the second number and then add the corresponding bits of both numbers.

•

$$A - B = A + (2^{n} - B)$$

0110 (6)

$\frac{+1100}{100}$  (-4)

$\frac{100}{100}$

• For example: 3 = 0011 - 2 = 00101 = 0001

## Overflow

- When adding or subtracting numbers, the sum or difference can go beyond the range of representable numbers.

- This is known as overflow. For example, for two's complement numbers,

- 5 = 0101 -5 = 1011

- + 6 = 0110 + -6 = 1010

-5 = 1011 5 = 0101

Overflow creates an incorrect result that should be detected.

## 2's Comp - Detecting Overflow

- When adding two's complement numbers, overflow will only occur if

- the numbers being added have the same sign

- the sign of the result is different

- If we perform the addition

$= S_{n-1} S_{n-2} \dots S_1 S_0$

Overflow can be detected as

$$V = a_{n-1} \cdot b_{n-1} \cdot \overline{s_{n-1}} + \overline{a_{n-1}} \cdot \overline{b_{n-1}} \cdot s_{n-1}$$

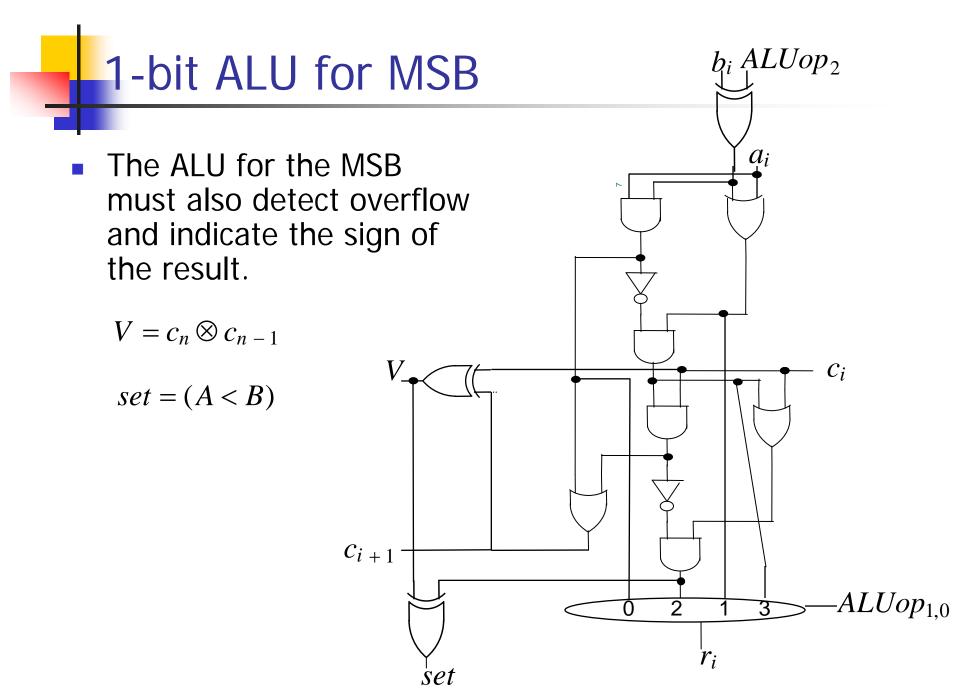

Overflow can also be detected as

$V = c_n \otimes c_{n-1}$ , where  $c_{n-1}$  and  $c_n$  are the carry in and carry out of the most significant bit.

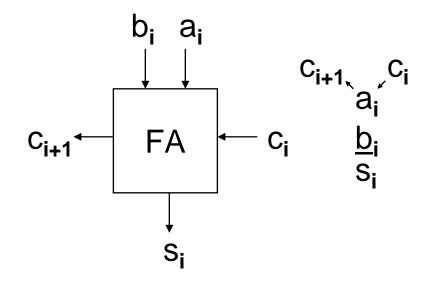

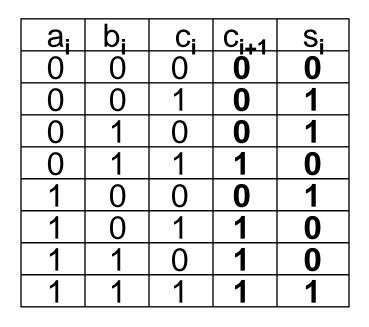

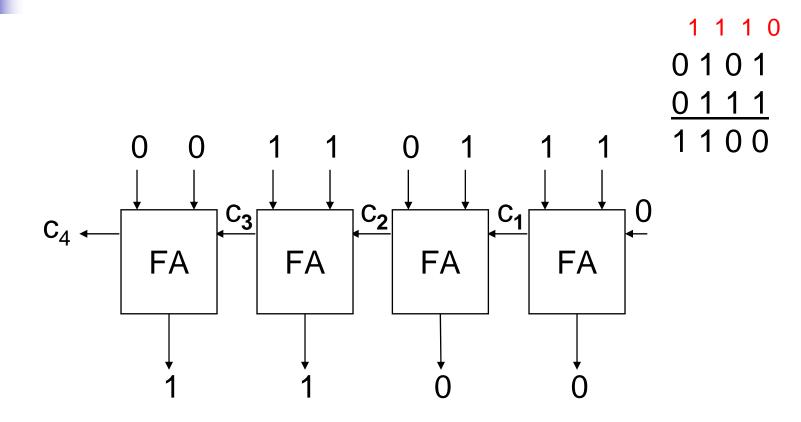

### Full Adder

- A fundamental building block in the ALU is a full adder (FA).

- A FA performs a one bit addition.

$a_{i}+b_{i}+c_{i}=c_{i+1}s_{i}$

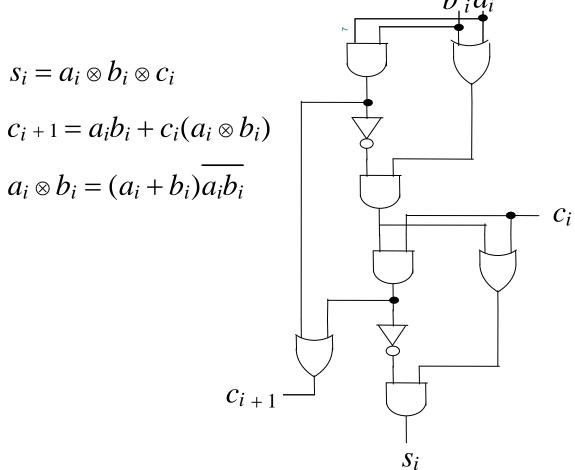

#### Full Adder Logic Equations

- s<sub>i</sub> is '1' if an odd number of inputs are '1'.

- c<sub>i+1</sub> is '1' if two or more inputs are '1'.

$$s_{i} = \overline{a_{i}b_{i}c_{i}} + \overline{a_{i}b_{i}c_{i}} + a_{i}\overline{b_{i}c_{i}} + a_{i}b_{i}c_{i}$$

$$s_{i} = a_{i} \otimes b_{i} \otimes c_{i}$$

$$c_{i+1} = \overline{a_{i}b_{i}c_{i}} + a_{i}\overline{b_{i}c_{i}} + a_{i}b_{i}\overline{c_{i}} + a_{i}b_{i}c_{i}$$

$$c_{i+1} = a_{i}b_{i} + a_{i}c_{i} + b_{i}c_{i}$$

$$c_{i+1} = a_{i}b_{i} + c_{i}(a_{i} + b_{i})$$

$$c_{i+1} = a_{i}b_{i} + c_{i}(a_{i} \otimes b_{i})$$

# Full Adder Design

One possible implementation of a full adder uses nine gates.

b<sub>i</sub>a<sub>i</sub>

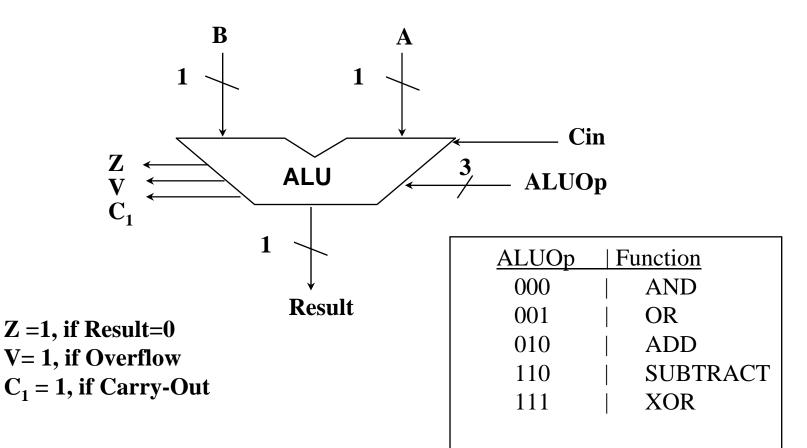

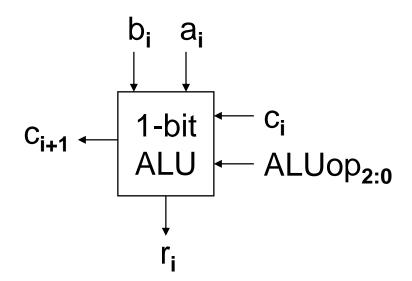

## ALU Interface

• We will be designing a 1-bit ALU with the following interface.

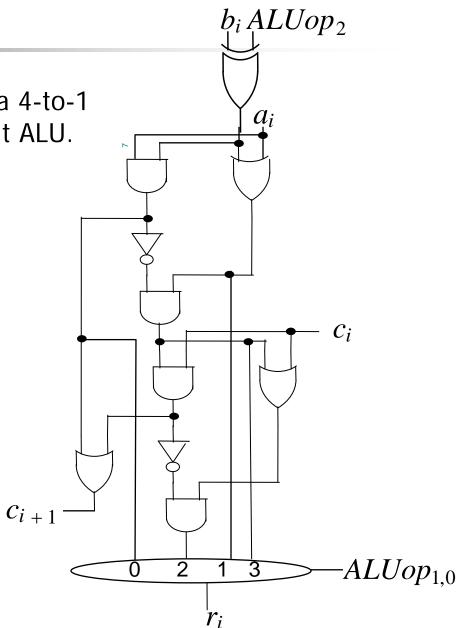

#### 1-Bit ALU

The full adder, an xor gate, and a 4-to-1 mux are combined to form a 1-bit ALU.

| <u>ALUOp</u> | F | <u>Sunction</u> |

|--------------|---|-----------------|

| 000          |   | AND             |

| 001          |   | OR              |

| 010          |   | ADD             |

| 110          |   | SUBTRACT        |

| 111          |   | XOR             |

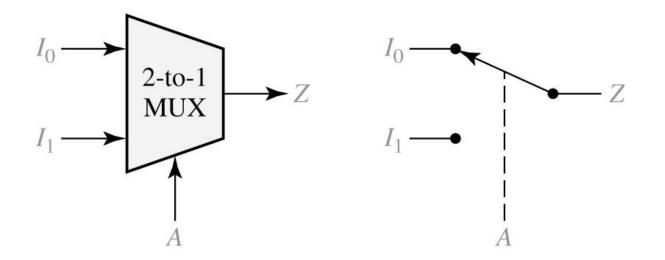

Fig 9-1. 2-to-1 Multiplexer and Switch Analog

logic equation for the 2 - to -1 MUX

$$Z = A'I_0 + AI_1$$

EE203 Digital System Design

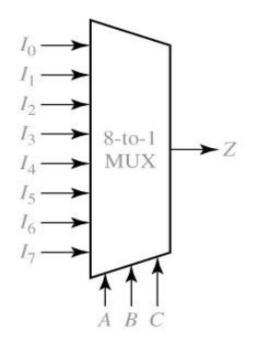

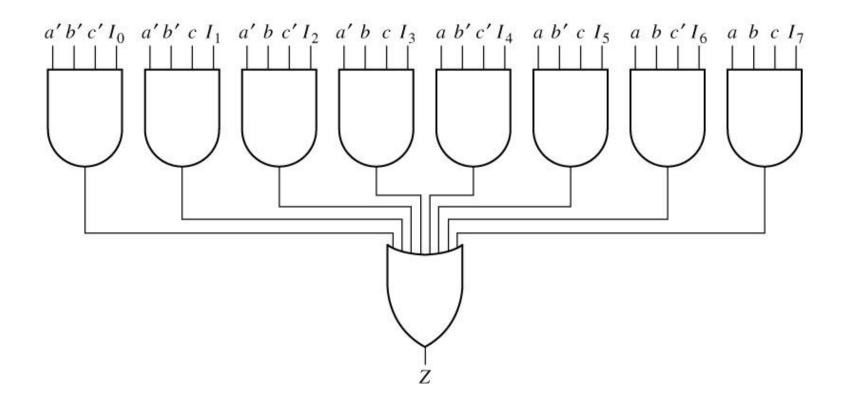

#### **Multiplexers**

#### Fig 9-2. Multiplexer (2)

logic equation for the 8-to-1 MUX

$Z = A'B'C'I_0 + A'B'CI_1 + A'BC'I_2 + A'BCI_3$  $+ AB'C'I_4 + AB'CI_5 + ABC'I_6 + ABCI_7$

Fig 9-3. Logic Diagram for 8-to-1 MUX

# Assembly Example

|       | .data                               |                      |   |                                |  |

|-------|-------------------------------------|----------------------|---|--------------------------------|--|

| str1: | .asciiz "                           | \nEnter a number for | S | ummation:"                     |  |

| str2: | .asciiz "Sum of numbers entered = " |                      |   |                                |  |

|       |                                     |                      |   |                                |  |

|       | .text                               |                      |   |                                |  |

|       | .globl main                         |                      |   |                                |  |

| main: |                                     |                      |   |                                |  |

|       | li \$t0, 0                          |                      |   |                                |  |

| loop: |                                     |                      |   |                                |  |

|       | li                                  | \$v0, 4              | # | system call code for print_str |  |

|       | la                                  | \$a0, str1           | # | address of string to print     |  |

|       | syscall                             |                      |   |                                |  |

|       | li                                  | \$v0, 5              | # | system call code for read_int  |  |

|       | syscall                             |                      | # | read int                       |  |

|       |                                     |                      |   |                                |  |

|       | add                                 | \$t0, \$t0, \$v0     |   |                                |  |

|       | bne                                 | \$v0, \$zero, loop   |   |                                |  |

|       |                                     |                      |   |                                |  |

|       | 1i                                  | \$v0, 4              | # | system call code for print_str |  |

|       | la                                  | \$a0, str2           | # | address of string to print     |  |

|       | syscall                             |                      |   |                                |  |

|       | li                                  | \$v0, 1              | # | system call code for print_int |  |

|       | move                                | \$a0, \$t0           | # | move the result in \$a0        |  |

|       | syscall                             |                      | # | print it                       |  |

|       |                                     |                      |   |                                |  |